University of Koblenz – Landau Faculty 4 Institute of Computer Science

# Apple ][ Emulation on an AVR Microcontroller

August 2014

Bachelor thesis to obtain the academic degree "Bachelor of Science (BSc)"

Submitted by:

Maximilian Strauch (Student ID: 211 201 869)

Supervised by:

Prof. Dr. Hannes Frey Dr. Merten Joost Fiat lux!

# Ehrenwörtliche Erklärung

Hiermit bestätige ich, dass die vorliegende Arbeit von mir selbständig verfasst wurde und ich keine anderen als die angegebenen Hilfsmittel – insbesondere keine im Quellenverzeichnis nicht benannten Internet–Quellen – benutzt habe und die Arbeit von mir vorher nicht in einem anderen Prüfungsverfahren eingereicht wurde. Die eingereichte schriftliche Fassung entspricht der auf dem elektronischen Speichermedium (CD-Rom).

|                                                                         | Ja | Nein |

|-------------------------------------------------------------------------|----|------|

| Mit der Einstellung der Arbeit in die Bibliothek bin ich einverstanden. | x  |      |

| Der Veröffentlichung dieser Arbeit im Internet stimme ich zu.           | ×  |      |

.....

(Ort, Datum)

(Unterschrift)

#### Apple ][ Emulation on an AVR Microcontroller

*Abstract* – The Apple ][ computer was one of the first three completely assembled systems on the market. It was sold several million times from april 1977 to 1993. This 8 bit home computer was developed by Steve Wozniak and Steve Jobs. They paved the way for the Apple Macintosh computer and the nowadays well known brand Apple with its products.

This thesis describes the implementation of a software emulator for the complete Apple ][ computer system on a single Atmel AVR microcontroller unit (MCU). The greatest challenge consists of the fact that the MCU has only a slightly higher clock speed as the Apple ][. This requires an efficient emulation of the CPU and the memory management, which will be covered later on along with the runtime environment controlling the emulator. Furthermore the hardware implementation into a handheld prototype will be shown.

In summary this thesis presents a successful development of a portable Apple ][ emulator covering all aspects from software design over hardware design ending up in a prototype.

*Keywords: Apple ][, emulation, Atmel AVR microcontroller*

#### Emulation eines Apple ][ auf einem AVR Microcontroller

*Zusammenfassung* – Der Apple ][ war einer der drei ersten kompletten Computersysteme auf dem Markt. Von April 1977 an wurde er rund 16 Jahre lang mehrere Millionen mal verkauft. Entwickelt wurde dieser 8 Bit Homecomputer von Steve Wozniak und Steve Jobs. Sie ebneten damit den Weg für den Macintosh und das heute gut bekannte Unternehmen Apple.

Diese Arbeit beschreibt die Implementierung eines Softwareemulators für das komplette Apple ][ Computersystem auf nur einem Atmel AVR Microcontroller. Die größte Herausforderung besteht darin, dass der Microcontroller nur eine geringfügig höhere Taktrate als die zu emulierende Hardware hat. Dies erfordert eine effiziente Emulation der CPU und Speicherverwaltung, die nachfolgend zusammen mit der Laufzeitumgebung für die Emulation vorgestellt wird. Weiterhin wird die Umsetzung des Emulators mit Display und Tastatur in Hardware näher erläutert.

Mit dieser Arbeit wird die erfolgreiche Entwicklung eines portablen Apple ][ Emulators, von der Software über die Hardware bis hin zu einem Prorotypen, vorgestellt.

Schlagworte: Apple ][, Emulator, Atmel AVR Microcontroller

# **Table of contents**

| Chapter 1: Preface                                                                                                                                                                                                    | . 5                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.1 Related work                                                                                                                                                                                                      | 8                                |

| 1.2 Structure                                                                                                                                                                                                         | 9                                |

| 1.3 Legal thoughts                                                                                                                                                                                                    | . 9                              |

| 1.4 Terminology                                                                                                                                                                                                       |                                  |

| Chapter 2: Essentials                                                                                                                                                                                                 | 11                               |

| 2.1 The Apple ][                                                                                                                                                                                                      | 11                               |

| 2.1.1 MOS Technology 6502                                                                                                                                                                                             | 12                               |

| 2.1.2 Memory organisation                                                                                                                                                                                             | 19                               |

| 2.1.3 Video output                                                                                                                                                                                                    | 22                               |

| 2.1.4 The keyboard                                                                                                                                                                                                    | 24                               |

| 2.1.5 Other hardware features                                                                                                                                                                                         | 25                               |

| 2.1.6 Software insights: System Monitor & BASIC                                                                                                                                                                       | 25                               |

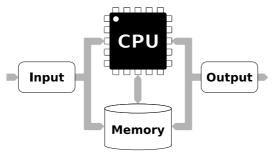

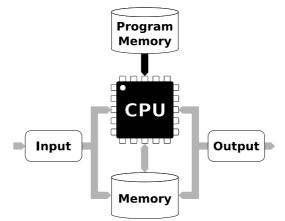

| 2.2 Microcontrollers vs. Microprocessors                                                                                                                                                                              | 26                               |

| 2.3 Different architectures                                                                                                                                                                                           | 27                               |

| 2.3.1 Von Neumann architecture                                                                                                                                                                                        | 27                               |

| 2.3.2 Harvard architecture                                                                                                                                                                                            | 27                               |

| Chapter 3: Software implementation                                                                                                                                                                                    | 29                               |

| 3.1 Concept and basic setup                                                                                                                                                                                           | 29                               |

| 3.2 Emulation of the MOS 6502 CPU                                                                                                                                                                                     | 30                               |

| 3.2.1 Requirements and exclusions                                                                                                                                                                                     | 30                               |

| 3.2.2 Designing the emulator – a simple approach                                                                                                                                                                      | 32                               |

| 3.2.3 Revision of the first approach                                                                                                                                                                                  | 35                               |

| 3.2.4 Internals of the instruction opcode implementations                                                                                                                                                             | 36                               |

| 3.2.5 Identifying other retardants                                                                                                                                                                                    | 39                               |

| 3.2.6 The memory access                                                                                                                                                                                               | 40                               |

| 3.2.7 First tests                                                                                                                                                                                                     | 43                               |

| 3.2.8 Going back to the roots                                                                                                                                                                                         | 44                               |

| 3.2.9 New speed measurements & summary                                                                                                                                                                                | 52                               |

| 3.3 The emulator runtime environment                                                                                                                                                                                  |                                  |

|                                                                                                                                                                                                                       | 53                               |

| 3.3.1 The structure                                                                                                                                                                                                   |                                  |

| 3.3.1 The structure<br>3.3.2 Display output of the emulator (module "Display")                                                                                                                                        | 54                               |

| 3.3.2 Display output of the emulator (module "Display")<br>3.3.3 Keyboard input (module "Keyboard")                                                                                                                   | 54<br>55<br>56                   |

| 3.3.2 Display output of the emulator (module "Display")                                                                                                                                                               | 54<br>55<br>56                   |

| 3.3.2 Display output of the emulator (module "Display")<br>3.3.3 Keyboard input (module "Keyboard")<br>3.3.4 Bringing software into the emulator (module "DSK I/O")<br>3.3.5 Hibernation feature (module "State I/O") | 54<br>55<br>56<br>58<br>61       |

| 3.3.2 Display output of the emulator (module "Display")<br>3.3.3 Keyboard input (module "Keyboard")<br>3.3.4 Bringing software into the emulator (module "DSK I/O")                                                   | 54<br>55<br>56<br>58<br>61<br>62 |

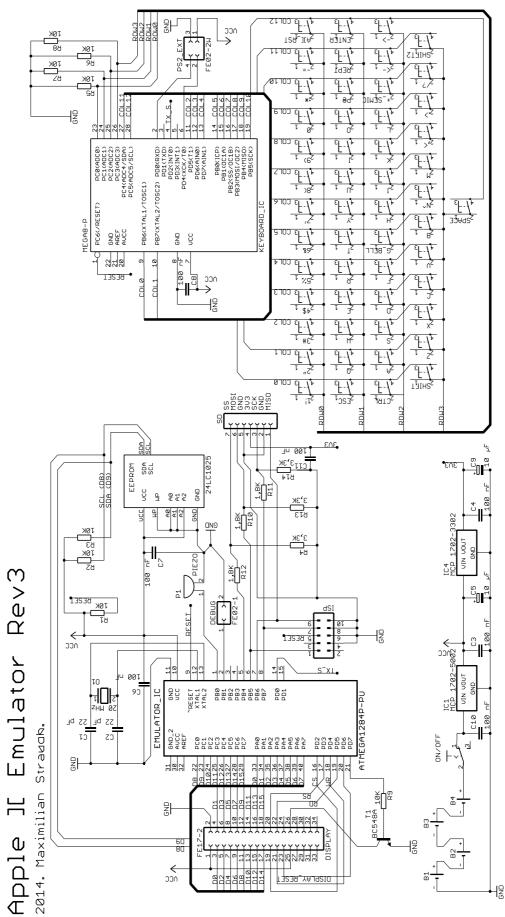

| Chapter 4: Hardware implementation   | 64 |

|--------------------------------------|----|

| 4.1 The "emulation" microcontroller  | 64 |

| 4.1.1 Pinout and pin mapping         | 65 |

| 4.1.2 Interfacing the display        | 66 |

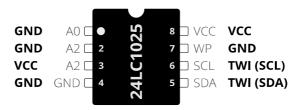

| 4.1.3 Talking to the EEPROM          | 69 |

| 4.1.4 The SD card and ISP connectors | 70 |

| 4.2 The "keyboard" microcontroller   | 72 |

| 4.2.1 Pinout                         | 72 |

| 4.2.2 Keyboard switch matrix design  | 73 |

| 4.2.3 Software UART transmit         | 74 |

| 4.2.4 Possible disadvantages         | 75 |

| 4.3 BOM                              | 75 |

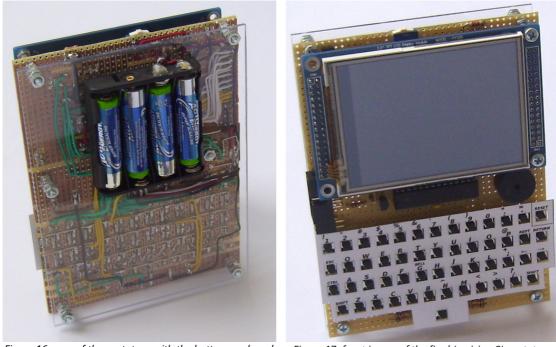

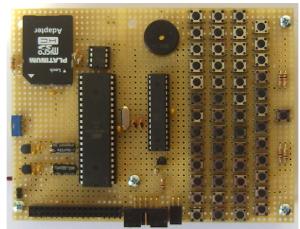

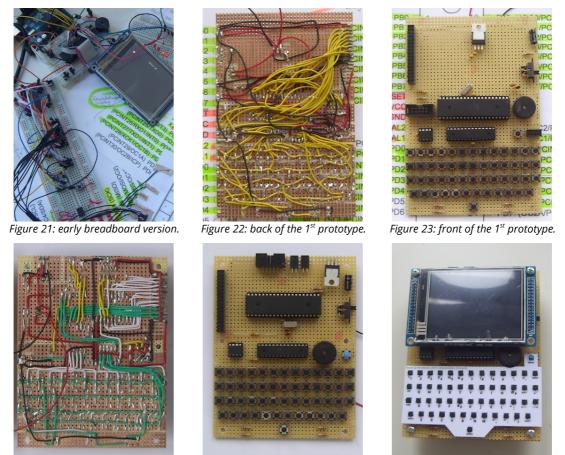

| 4.4 The prototype                    | 77 |

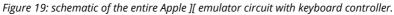

| 4.5 Schematic of the prototype       | 78 |

| Chapter 5: Conclusion & Outlook      | 80 |

| 5.1 Conclusion                       | 80 |

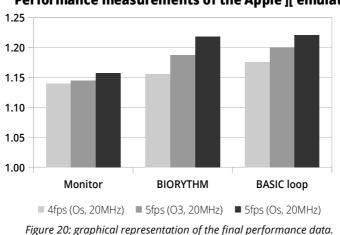

| 5.1.1 Achieved emulator speed        | 82 |

| 5.1.2 Unmentioned aspects            | 83 |

| 5.2 Further development              | 84 |

| Chapter 6: Appendix                  | 86 |

| 6.1 Glossary                         | 86 |

| 6.2 Bibliography                     | 89 |

| 6.3 "Speed" measurement setup        | 91 |

# **Chapter 1: Preface**

#### Introduction

The market of microcontrollers grows from year to year and expanded in the last ten years by 80% [1]. Those tiny devices, equipped with everything a modern computer contains, manage many things in our daily life. Because of the fact that they are based on a  $\rightarrow$ RISC instruction set architecture,  $\rightarrow$ microcontrollers are so powerful that the question arises whether it can emulate an entire historical personal computer.

A very interesting personal computer is the Apple ][, which was build by Steve Wozniak together with Steve Jobs and sold from the beginning of the late 70<sup>th</sup>. It was a very popular and powerful system, providing very sophisticated graphical and technical features for this time. Together with two other computer systems, it was the first complete assembled computer system commercially available. Other computer systems were only available as self-assembly kits and not so powerful. It was build upon an 8 bit architecture, using the – for those days – famous MOS Technologies 6502  $\rightarrow$ microprocessor (CPU), which was widely used in many computer related devices in the late 70<sup>th</sup> and 80<sup>th</sup>. Famous devices that make use of the 6502 are: the Apple ][ computer series, the Atari 2600 game console, Nintendo NES game console (slightly modified 6502 model), the Commodore VIC-20 and many other devices [2].

Since the aimed device does not only emulate the 6502 microprocessor, but also perform display output and other I/O to achieve an emulation of the entire computer system by a microcontroller, it is too complex to evaluate it, using a theoretical model. The research question is therefore not only to find out, if it is possible, but also to find out the limitations which arise.

#### Motivation

This project provides the feasibility to investigate the facets of hardware related computer science. This part plays an important role in the everyday life of everybody. Tiny, embedded devices like microcontrollers are embedded in nearly every electronic device. From the washing machine over the electronic radiator thermostat to a car. Inside the play field of microcontroller devices one can learn and understand easily, how modern computers work and see, by example, the basic concepts of computers. This "experiments" can be done very easily on microcontrollers, because they are very simple in structure and so it is easy to get started in comparison to the x86 system architecture. In addition to this, one will discover different aspects of communication between electronic devices and learn to understand and use protocols like:  $\rightarrow$ UART,  $\rightarrow$ SPI or  $\rightarrow$ TWI. Those protocols are not limited to the world of microcontrollers: computers rely on this protocols by example to monitor the processor temperature using sensors, which stream the data through the TWI protocol to the CPU. Or more famous: the SD card can be accessed through the SPI protocol. This leads to the fact that the world of microcontrollers is important for modern hardware and devices. By getting an insight into this "world", one is capable of understanding computers and their structure even better.

Developing a handheld device from scratch, which can be hold in one's own hands and driven without the need of a computer, makes software real and touchable. Combining this with a recreation of a historical important device, like the Apple ][, allows to preserve nostalgia and brings the history of computer science to the present.

By learning many things about computers, microcontrollers and their structure and creating a handheld device from scratch, to take a look into the early days of computers and their usage, this is an ideal project for the purpose of an bachelor thesis.

#### What is emulation? And what's new with that?

Emulation is the process of a very precise simulation of original hardware, in order to use software which was compiled for the original hardware, through the emulation on different hardware which is incompatible [3].

In this case, the software written for the Apple ][ computer only works on exactly this processor which was used by the Apple ][. By creating an emulator of the Apple ][ one needs to simulate the processor in order to let the software, written for the Apple ][, work on the emulator which runs on a completely different hardware.

But there is nothing new: by browsing through the world wide web one can find more than enough emulators for all kinds of historical devices and also Apple ][ emulators. These emulators work on a computer with a lot of computational power and they are not very portable.

The idea of this thesis is to create an emulator in software and hardware, especially designed only for the emulation of the Apple ][ system. The created device should be a "handheld" device which is portable. The used microcontroller to run the emulator relies – just like the Apple ][ – on an 8 bit architecture and has only a slightly faster clock of 20 MHz versus 1 MHz of the Apple ][.

There is no doubt that the emulator works with a normal computer, decreeing over multiple cores and many giga hertz of CPU speed. An important question is if the emulation will work on a tiny microcontroller, which is only twenty times faster than the emulated host, the Apple ][. And the device will not be finished with the emulation of the Apple ][ microprocessor. Display output, keyboard input and some other features need to be implemented to make the device useable.

Talking about emulation is talking about speed. By recreating the hardware of the Apple ][ with a software emulator, control overhead data is generated, which must be processed and stored. The more sophisticated the architecture is, the more overhead is generated and the calculation time grows.

Besides the software part, this thesis features also the hardware implementation pro-

cess of creating a physical device, using skills like soldering and building, facing different problems which will arise from the electronic part of the project.

#### FPGAs as competitors?

A  $\rightarrow$  FPGA can be used to less emulate but more **"be"** the target CPU of any device, by example the Apple ][ computer. It can also imitate an entire system consisting of multiple microchips. And it was already used by different projects aiming an emulation of the Apple ][, which can be found in the world wide web [4].

The "field programmable gate array" (FPGA) is a "programmable" integrated circuit. Using a computer program a logical circuit, out of discrete logical gates, is created and then programmed or build to the FPGA chip. After programming the FPGA actually *is* the circuit, designed on the computer and realizes it in hardware. This allows various projects and also the perfect imitation – not emulation, because it is rebuilt out of discrete logical components – of CPUs [5] (p. 21).

As seen by this brief introduction, FPGAs are a lot more powerful than microcontrollers and can be used for sophisticated tasks like realtime image processing, by example. Beside the fact that they are more cost intensive, the aim of this thesis is to use a microcontroller to get an idea of how far the computational power can be lowered to emulate the system. But it is also a challenge of costs, aiming to construct a device which uses less components and is as cheap as possible.

#### Other embedded systems

Modern devices, like cell phones or tablets are using mostly  $\rightarrow$  ARM processors. Those are also available as chips to develop embedded applications. But they are baed on a 32 bit architecture and there is – just like the FPGAs – no motivation to try this project with such a sophisticated architecture, because there is no challenge to develop the emulation software and face problems. One could simply bring a Linux system onto this chip and run emulator software from the web.

#### **Demand profile**

Due to the fact that this project is a thesis with the aim of an Apple ][ emulator, some requirements were defined at the beginning of the project to ensure a high quality result.

First of all, the overall target of this thesis is to build an emulator handheld device of the original Apple ][ model from 1977 with a memory configuration of 12KB<sup>1</sup>. The other key requirements are:

- implementation of a 6502 microprocessor *without* the decimal mode in C or assembly language

- interfacing a TFT display with video RAM

- sketching a custom keyboard with controller

- realization the Von Neumann architecture on the Harvard architecture of the microcontroller

<sup>1</sup> This restriction will be discussed in section 3.1 "Concept and basic setup", subsection "Hardware limitations" (p. 30).

- implementation of different memory accesses (RAM, ROM, I/O)

- software loading possibility (for programs written for the Apple ][)

- buildup as a mobile handheld system

- documentation of the result

Those requirements are evaluated in detail on the end of this work with the gathered results in chapter 5 "Conclusion & Outlook" (p. 80).

### 1.1 Related work

After an advanced research, only two other projects could be found, which rebuild the Apple ][ computer system – or parts of it – on an microcontroller, especially an AVR microcontroller (which will be used later on). Both were implemented at the Cornell University (Ithaca, NY, United States of America) during the course "ECE 4760: Designing with Microcontrollers" [6].

In the year 2007, three students from Cornell University tried to develop a system, which is able to emulate the Apple ][ computer on an Atmel AVR ATMega32 microcontroller, in a practicum [7]. Because of the fact that they had not enough time to finish their project and had some issues with the memory subsystem, only a working MOS 6502 microprocessor emulator, a memory subsystem and a partial GPU (graphic processing unit) was created by them without reaching the desired Apple ][ emulator system. The difference to this thesis is not only the fact that this thesis creates a running device, but also that this thesis creates a fully self-contained Apple ][ emulator with less hardware components and equipped with a display to be portable.

Later on, in the year 2009, another team of two students tried to create an emulation of the NES (Nintendo Entertainment System) [8]. Despite the fact that this project was not led to the target of a complete NES emulation, which is hardly at the upper end of the possibilities of the Atmel AVR microcontroller due to the complex PPU, this project shares only the MOS 6502 processor emulation with this project.

Other MOS 6502 microprocessor emulations, based on an AVR microcontroller, are available on the world wide web [9] (only *one* example page). The most MOS 6502 microprocessor emulations found on the web are written in C or C with inline assembler and not highly optimized which will turn out as a key factor later on. Because of this fact, using an existing 6502 microprocessor emulator is not an option.

During further research, it turned out that – to the knowledge of the author – nobody had ever tried the target of this project: to create a portable Apple ][ emulator handheld device. The shown other projects did not reach their target and result in an unusable emulator device. So the results might only be used for initial design but not for real implementation purposes.

Furthermore there is no indicator that anybody has created an Apple ][ computer system emulator combining a custom keyboard, display, batteries and the microcontroller in one single device that can be carried around in a pocket. And this is exactly the desired result of this thesis. Due to this fact, the proposed solution of this thesis is a premiere.

### **1.2** Structure

This thesis features the entire way of producing a final product, which would be done by companies: from the idea over first thoughts to the software development and finally the implementation of a working prototype. The document is structured as follows.

First of all the structure and details of the Apple ][ computer system and the MOS Technology 6502 microprocessor are explained in chapter 2 (p. 11). Due to the fact that one needs to know all the details of the microprocessor or Apple ][ system to emulate it, those are deeply covered. Then the implementation of the emulator software is described in chapter 3 (p. 29). Thereby some first considerations for the hardware of the resulting device are made, since the software implementation of the emulator is limited by hardware details of the used microcontroller. This chapter not only describes the implementation of the 6502 microprocessor emulation, it also describes other parts of the emulator runtime environment which manages the emulator. In chapter 4 (p. 64) the software implementation is supplemented by hardware implementation details, forming the aimed portable handheld Apple ][ emulator (chapter 4.4 "The prototype", p. 77). Finally, this thesis is closed with a conclusion of the achieved targets: it takes an outlook to new features which might be implemented to advance the resulting handheld device in chapter 5 (p. 80).

# 1.3 Legal thoughts

Emulating a system opens the question of legitimacy. In this particular case, there is no reason for concern. To the knowledge of the author, the MOS 6502 was not patented itself but some features were, like the on-the-fly correction of binary adding results which was registered on the 16<sup>th</sup> september 1975 [10] (US patent: US 3991307 A). Since this patent lasts up to 20 years and MOS Technologies no longer exists, there is most likely no active copyright left [11]. One should also not overlook that this work has exclusively an educational purpose.

Furthermore the software and operating system of the Apple ][ is the critical component, since this parts are copyrighted by Apple Inc. and others. A usage of this software might not be allowed. But since a marvellous "donation" from Apple Inc. to the Computer History Museum in Mountain View (CA, United States of America) the source code was made available for non-commercial use at the end of 2013:

With thanks to Paul Laughton, in collaboration with Dr. Bruce Damer, founder and curator of the DigiBarn Computer Museum, and with the permission of Apple Inc., we are pleased to make available the 1978 source code of Apple II DOS for non-commercial use. This material is Copyright © 1978 Apple Inc., and may not be reproduced without permission from Apple [12].

The downloads contain various documents related to the Apple ][ development and the source code for the Apple ][ DOS and BASIC.

(Thanks, Apple!)

# 1.4 Terminology

To prevent misunderstandings and irritations some terms, symbols and spellings are expounded in the following:

- if furthermore memory sizes are meant, "K" is an abbreviation for "kilobyte". So the term "8K" stands for 8 kilobyte of data (8.192 byte).

- strings starting with "0x" indicate a hexadecimal number. Strings starting with "0b" indicate a binary number. An asterisk "\*" in a binary or hexadecimal number indicates a placeholder for any value of this number system, e.g. 0xf\* stands for numbers from 0xf0 to 0xff. If there is no such notation, the numbers are noted in the standard decimal system to base ten.

- humans tend to start counting by one. On everything related to technical topics, numbering starts by zero. This is the way, how numbering is handled in this document. Be aware of the fact that ordinal numbers still start by one.

- all abbreviations or words with a " $\rightarrow$ " character in front have a short explanation inside the glossary on page 86.

- a number in square brackets represents a literature reference, which can be followed by a page number inside the referenced literature (p. 89). By example the reference "[42] (p. 43)" references literature number 42. A following page number points to the particular page *of the literature*, where the referenced information can be found in this example on page 43.

# **Chapter 2: Essentials**

This chapter reveals a detailed view of the Apple ][ computer system featuring especially the CPU as an important component for the emulation. Understanding the structure and behaviour of the CPU is fundamental for the following chapters of this thesis so all important facts are explained here. The historical context is described very shortly – see referenced literature for more historical details.

# 2.1 The Apple ][

After a successful presentation of the Apple I computer, which was built by Steve Wozniak and published together with Steve Jobs in April 1976, the series was continued. Finally in April 1977 the Apple ][ was published [13] (p. 20). Together with two other home computer devices, it was the first computer system which came fully assembled. It was sold from 1977 to 1993, around 16 years, two million times [13].

Figure 1: Apple ][ computer with monitor at the Museum Of The Moving Image in New York City<sup>2</sup>.

During the 16 years of production, the system was extended multiple times. Initially the Apple ][ "original" was released in 1977 with the Apple Integer BASIC, written by Steve Wozniak in around six weeks, missing floating point arithmetics due to time constraints [13]. After that the Apple ][+ was published in 1979 with an Applesoft BASIC, written by Microsoft and including the desired floating point arithmetics [12]. Also the Disk ][ - the floppy disk drive – was integrated by the software, so that the system could automatically boot during startup from an inserted floppy disk. In the year 1983, the Apple //e was launched. It contained a more sophisticated graphic output, could be extended from 64K to 128K and the input of lower case characters was possible [13] (p. 41). Around the release date of this model, the Apple ][c and Apple ][c+ were released in 1984. It was a compact version of the Apple //e with a weight of around 4 kg

<sup>2</sup> Image source: Marcin Wichary, CC BY 2.0, recorded on 30th december 2007, accessed on 6th june 2014, http://www.flickr.com/photos/mwichary/2151368358/.

[13] (p. 49). In 1986, the Apple IIGS was the final successor of the Apple ][ series, completing this successful computer series [13] (p. 57). The Apple IIGS disposed extended graphics and sound capabilities with the possibility of running original programs for the Apple ][ on the one hand and the graphical user interface of the Apple Macintosh series, which was started in 1984, on the other hand [13] (p. 47). The major difference to the Apple Macintosh was the fact, that the Apple IIGS provided a colored output instead of the black-and-white output of the Apple Macintosh computer until this date [13]. This last Apple ][ model was moreover the last model which was designed under assistance of Steve Wozniak, who stopped his active membership as a developer for Apple in february 1985 [13] (p. 51).

# 2.1.1 MOS Technology 6502

The main part of the Apple ][ computer is the 6502 microprocessor, designed by Chuck Peddle and Bill Mensch at MOS Technology [14]. As the market and interests on microprocessors started in the 70<sup>th</sup>, Intel and Motorola as leading companies developed their own microprocessors like the Intel 8080 or the Motorola 6800. All these microprocessors were full featured 8 bit machines with a wide variety of use. The prices for one of these new microprocessors were fairly high, based at around \$300 for the Intel 8080 with some support chips [14].

When the 6502 was introduced, in 1975, it cost about one-sixth of the other models, available on the market. So it became the least expensive but full-featured 8 bit micro-processor one can buy these days [14]. So the 6502 was a little revolution for the microprocessor market. This was the key fact which improved the popularity of the 6502 very fast.

#### **Technical overview**

In order to get an overview over the technical features of the MOS 6502 microprocessor, bellow some important data are listed [15]:

- single +5V power supply in difference to the Intel 8080 with –5V, +5V and +12V power supply [16]

- 8 bit parallel processing with 56 instructions and basic support for pipelining

- 13 addressing modes, available for nearly all instructions

- hardware based decimal and binary arithmetics

- addressable memory up to 65K

- clock frequency between 1MHz and 2 MHz

- between two and seven machine cycles per instruction

- between one and three bytes instruction length

- →little endian byte encoding

- three hardware interrupts and one software interrupt

- register files:

- Accumulator (8 bit)

- X, Y as 8 bit index registers; used for addressing

- PC as 16 bit program counter

- SP as 16 bit stack pointer with the most significant byte hard wired to 0x01, so that the stack is 256 byte wide from 0x01ff to 0x0100

- P as processor status register

Some important parts of the processor will be covered by the following sections in detail.

#### **Memory map**

The MOS 6502 processor is able of addressing 64K bytes of memory. The processor stack, interrupt vectors and the zero page are placed at determined locations [15] [17]:

- 0x0000 0x00ff: zero page. The first 256 bytes of memory are called "zero page". These locations are used to speed up programs. As a normal addressing mode would take two bytes as instruction operands to address the whole 64K memory, it takes also many clock cycles. Using zero page addressing it is possible to speed up programs [17] (p. 61). By placing absolute addresses or even values in this first memory page, instructions only need to fetch one argument. Therefor the execution can be done faster. All other addressing modes will be covered later in section "Addressing modes" (p. 14).

- 0x0100 0x01ff: stack. The processor stack is placed on the second memory page. This results in 256 bytes of stack size, which grows from the greatest memory location (0x01fff) down to the lowest and wraps around to the top if it overflows.

- 0xfffa 0xffff: **interrupt vectors**. These six memory locations form three 16 bit pointers into the memory. If an interrupt occurs the new program counter will be fetched from one of these locations (see p. 16)

While the zero page and interrupt vectors are intended to be overwritten and used by the application, the stack needs to be untouched for a proper code execution.

#### **Processor status register**

The status register contains seven single bit flags which are set or cleared when the instruction is executed. The following table explains the flags [15] [17]:

| Bit | Flag | Description                                                                                                                               |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | С    | Is set if the last instruction resulted in an over-<br>flow. It is used to perform addition and sub-<br>traction with more than one byte. |

| 1   | Z    | Set if the last result was zero or equal.                                                                                                 |

| 2   | I    | If set the system will not respond to the IRQ in-<br>terrupts. (The NMI cannot be masked out.)                                            |

| 3   | D    | If set the operations ADC and SBC will be set to                                                                                          |

| Bit | Flag | Description                                                                                              |

|-----|------|----------------------------------------------------------------------------------------------------------|

|     |      | decimal mode, working with binary coded decimals ( $\rightarrow$ BCD).                                   |

| 4   | В    | Indicates that the BRK instruction was exe-<br>cuted. This flag cannot be changed program-<br>matically. |

| 5   | 1    | Unused flag for later expansion. Mostly set to logical high level [15] [17].                             |

| 6   | V    | Is used to indicate whether the result can be expressed in 7 bits with a sign bit.                       |

| 7   | Ν    | Negative flag, indicating whether bit 7 of the result is set or not                                      |

Table 1: detailed description of the 6502 status register [15].

The flags are set by instructions and some flags can be directly set or cleared by the program. They are used directly for branch instructions and influence indirectly the executed arithmetic and logic instructions.

#### Addressing modes

The 6502 supports thirteen different addressing modes. Not each of the 56 instructions can be used with all these addressing modes, so that 151 valid opcodes are the result. The following table explains all addressing modes [17]:

| Mode (abbr.)                    | Description                                                                                                                                                                                                                    | Example                                                                                                                                     |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Accumulator<br>(accu)<br>1 byte | The value of the accumulator regis-<br>ter will be used as operand.                                                                                                                                                            | LDA #\$15<br><b>ASL A</b><br><i>The accumulator register will contain the</i><br><i>value</i> 0x2a <i>and the carry flag is cleared.</i>    |

| Implied<br>(impl)<br>1 byte     | The instruction needs no value to operate with or on; e.g. the status register is used.                                                                                                                                        | <b>CLC</b><br><i>The carry flag is cleared.</i>                                                                                             |

| Relative<br>(rel)<br>2 byte     | Only used with branch instructions:<br>the 2 <sup>nd</sup> byte is the branch displace-<br>ment, ranging from -128 to 127. The<br>decision of branching is made upon<br>the state of the intended the status<br>register flag. | <pre>infinite_loop_1:<br/>LDA #\$0<br/>BEQ infinite_loop_1<br/>If zero is loaded the zero flag is set. A Branch<br/>will be executed.</pre> |

| Immediate<br>(imm)<br>2 byte    | The operand is located in the 2 <sup>nd</sup> byte of the instruction.                                                                                                                                                         | LDA #\$42<br><b>AND #\$2a</b><br><i>The accumulator register will contain the</i><br><i>value</i> 0x02.                                     |

| Mode (abbr.)                             | Description                                                                                                                                                                                                                                      | Example                                                                                                                                                                             |  |  |  |  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Indexed<br>Indirect<br>(indX)<br>2 byte  | The sum of the second byte and the<br>value of the X register point to a<br>memory location in the zero page<br>where a 16 bit address is located,<br>which points to the final location.<br>Wraparound is used to stay inside<br>the zero page. | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                               |  |  |  |  |  |  |

| Indirect<br>Indexed<br>(indY)            | The second byte points into the zero<br>page where a 16 bit pointer is<br>located. The sum of the 16 bit<br>pointer and the value of the Y<br>register point to the intended<br>memory location.                                                 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                               |  |  |  |  |  |  |

| 2 byte<br>Zero Page<br>(zp)<br>2 byte    | Allows working with an operand in<br>the zero page by only specifying the<br>lower byte of the memory location<br>pointer. The upper byte is $0 \times 00$ . This<br>saves one instruction operand and<br>also execution cycles.                 | $0 \times 0015  0 \times 8080  0 \times 8081$ $0 \times 29  0 \times 6  0 \times 15$ After execution $0 \times 0015$ contains $0 \times 2a$ $(0 \times e6  0 \times 15 = INC $15).$ |  |  |  |  |  |  |

| Zero Page X<br>(zpX)<br>2 byte           | Points to a memory value inside the zero page. The pointer is the sum of the second instruction byte and the X register.<br>The sum wraps around at 0x00ff to remain in the zero page.                                                           | $0x0015  0x8080  0x8081$ $0x29  0xf6  0x11$ $0x29  0xf6  0x11$ $0x0015  0x004$ After execution $0x0015  contains  0x2a$ $(0xe6  0x15 = INC \ $15, X).$                              |  |  |  |  |  |  |

| Zero Page Y<br>(zpY)<br>2 byte           | Same behaviour as Zero Page X<br>addressing mode, but with Y register<br>instead of X. Supported by: LDX & STX.                                                                                                                                  | See Zero Page X with Y register.                                                                                                                                                    |  |  |  |  |  |  |

| Absolute<br>(abs)<br>3 byte              | The second and third byte specify an<br>absolute memory address, lower<br>byte first.<br>Thus, the complete 64K memory is<br>addressable.                                                                                                        | 0x2a15 0x8080 0x8081 0x8082<br>0x41 0xee 0x15 0x2a<br>After execution 0x2a15 contains 0x42                                                                                          |  |  |  |  |  |  |

| Absolute X<br>(absX)                     | The second and third byte point to a<br>memory location in the 64K memory.<br>The final pointer consists of the sum<br>of the 16 bit pointer and the value of<br>the X register.                                                                 | (0xee 0x15 0x2a = INC \$2a15)<br>0x2a15 0x8080 0x8081 0x8082<br>0x41 0xfe 0x11 0x2a<br>After execution 0x2a15 contains 0x42<br>(0xfe 0x11 0x2a = INC \$2a15, X).                    |  |  |  |  |  |  |

| 3 byte<br>Absolute Y<br>(absY)<br>3 byte | Same behaviour as "Absolute X"<br>addressing mode, but with the Y<br>register instead of X.                                                                                                                                                      | See Absolute X with Y register.                                                                                                                                                     |  |  |  |  |  |  |

| Mode (abbr.)                            | Description                                                                                                                                                                                                  | Example                                                                                                                                |  |  |  |  |  |  |  |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Absolute<br>Indirect<br>(ind)<br>3 byte | The two instruction operands point<br>to an address in memory where an<br>other 16 bit pointer is located, which<br>points to the intended memory<br>location.<br><i>This mode is only supported by JMP.</i> | 0x2a15 0x2a16 0x3433 0x8080 0x8081 0x8082<br>0x33 0x34 0xea 0x6c 0x15 0x2a<br>After execution the PC points to 0x3433<br>(0x6c = JMP). |  |  |  |  |  |  |  |  |  |

Table 2: detailed explanation of all different addressing modes supported by the MOS 6502 microprocessor.

Please note that the explanations in table 2 assume that an instruction consists at least of one byte, the instruction opcode itself. The following two operands or arguments are optional.

#### **Instruction overview**

Table 3 (p. 17) gives a simple outline of all the instruction opcodes available on the MOS 6502 microprocessor along with their specifications (addressing mode, length in byte, cycle count).

In every cell of the table the mnemonic of the instruction is displayed, followed by the addressing mode from table 2 and finally followed by the instruction length in bytes and the number of cycles this instruction takes. Empty fields are "illegal" opcodes.

As indicated by the asterisks, there are special rules for the number of cycles, which are taken by specific instructions:

- \* all cycle times labeled with a single asterisk take one more clock cycle if a page boundary in memory is crossed. This means if the final composed memory address crosses a page boundary, e.g. low byte on 0x2aff and high byte on 0x2b00, the additional cycle is added.

- \*\* (only branch instructions) since a branch has several possibilities to perform, there are different cycle consumptions: a branch not taken requires the standard two cycles. If the branch is taken, it requires three clock cycles. And if it is taken and crosses a page boundary, it requires four cycles.

The remaining 105 instructions – represented by an empty cell in table 3 – are not explained in this document but they have some function, indeed. The problem here is that they are "illegal". The manufacturer has not given any sense to this instructions and also not tied them to something like a "no operation". Instead they all do some fancy things on a real MOS 6502 microprocessor. Some illegal instructions perform stable operations, like a double NOP. Others have an unpredictable behaviour, which can freeze the microprocessor. Hobbyist carried out tables of illegal instructions that seem to perform stable actions. Despite this, they are not covered in the official documents and also not in this document.

#### Interrupts

The interrupt feature is used to let the processor suspend the current sequential execution and jump to another code fragment. This interrupt event can be triggered by hardware and software and needs immediate attention. By example a keyboard input, which needs to be processed.

|      | 0x00                              | 0x01                           | 0x02                         | 0x03 | 0x04                         | 0x05                         | 0x06                         | 0x07 | 0x08                          | 0x09                           | 0x0a                          | 0x0b | 0x0c                           | 0x0d                           | 0x0e                           | 0x0f |

|------|-----------------------------------|--------------------------------|------------------------------|------|------------------------------|------------------------------|------------------------------|------|-------------------------------|--------------------------------|-------------------------------|------|--------------------------------|--------------------------------|--------------------------------|------|

| 0x00 | <b>BRK</b><br>(impl)<br>1 / 7     | <b>ORA</b><br>(indX)<br>2 / 6  |                              |      |                              | <b>ORA</b><br>(zp)<br>2 / 3  | <b>ASL</b><br>(zp)<br>2 / 5  |      | <b>PHP</b><br>(impl)<br>1 / 3 | <b>ORA</b><br>(imm)<br>2 / 2   | <b>ASL</b><br>(accu)<br>1 / 2 |      |                                | <b>ORA</b><br>(abs)<br>3 / 4   | <b>ASL</b><br>(abs)<br>3 / 6   |      |

| 0x10 | <b>BPL</b><br>(rel)<br>2 /<br>2** | <b>ORA</b><br>(indY)<br>2 / 5* |                              |      |                              | <b>ORA</b><br>(zpX)<br>2 / 4 | <b>ASL</b><br>(zpX)<br>2 / 6 |      | <b>CLC</b><br>(impl)<br>1 / 2 | <b>ORA</b><br>(absY)<br>3 / 4* |                               |      |                                | <b>ORA</b><br>(absX)<br>3 / 4* | <b>ASL</b><br>(absX)<br>3 / 7  |      |

| 0x20 | <b>JSR</b><br>(abs)<br>3 / 6      | <b>AND</b><br>(indX)<br>2 / 6  |                              |      | <b>BIT</b><br>(zp)<br>2 / 3  | <b>AND</b><br>(zp)<br>2 / 3  | <b>ROL</b><br>(zp)<br>2 / 5  |      | <b>PLP</b><br>(impl)<br>1 / 4 | <b>AND</b><br>(imm)<br>2 / 2   | <b>ROL</b><br>(accu)<br>1 / 2 |      | <b>BIT</b><br>(abs)<br>3 / 4   | <b>AND</b><br>(abs)<br>3 / 4   | <b>ROL</b><br>(abs)<br>3 / 6   |      |

| 0x30 | <b>BMI</b><br>(rel)<br>2 /<br>2** | <b>AND</b><br>(indY)<br>2 / 5* |                              |      |                              | <b>AND</b><br>(zpX)<br>2 / 4 | <b>ROL</b><br>(zpX)<br>2 / 6 |      | <b>SEC</b><br>(impl)<br>1 / 2 | <b>AND</b><br>(absY)<br>3 / 4* |                               |      |                                | <b>AND</b><br>(absX)<br>3 / 4* | <b>ROL</b><br>(absX)<br>3 / 7  |      |

| 0x40 | <b>RTI</b><br>(impl)<br>1 / 6     | <b>EOR</b><br>(indX)<br>2 / 6  |                              |      |                              | <b>EOR</b><br>(zp)<br>2 / 3  | <b>LSR</b><br>(zp)<br>2 / 5  |      | <b>PHA</b><br>(impl)<br>1 / 3 | <b>EOR</b><br>(imm)<br>2 / 2   | <b>LSR</b><br>(accu)<br>1 / 2 |      | <b>JMP</b><br>(abs)<br>3 / 3   | <b>EOR</b><br>(abs)<br>3 / 4   | <b>LSR</b><br>(abs)<br>3 / 6   |      |

| 0x50 | <b>BVC</b><br>(rel)<br>2 /<br>2** | <b>EOR</b><br>(indY)<br>2 / 5* |                              |      |                              | <b>EOR</b><br>(zpX)<br>2 / 4 | <b>LSR</b><br>(zpX)<br>2 / 6 |      | <b>CLI</b><br>(impl)<br>1 / 2 | <b>EOR</b><br>(absY)<br>3 / 4* |                               |      |                                | <b>EOR</b><br>(absX)<br>3 / 4* | <b>LSR</b><br>(absX)<br>3 / 7  |      |

| 0x60 | <b>RTS</b><br>(impl)<br>1 / 6     | <b>ADC</b><br>(indX)<br>2 / 6  |                              |      |                              | <b>ADC</b><br>(zp)<br>2 / 3  | <b>ROR</b><br>(zp)<br>2 / 5  |      | <b>PLA</b><br>(impl)<br>1 / 4 | <b>ADC</b><br>(imm)<br>2 / 2   | <b>ROR</b><br>(accu)<br>1 / 2 |      | <b>JMP</b><br>(ind)<br>3 / 5   | <b>ADC</b><br>(abs)<br>3 / 4   | <b>ROR</b><br>(abs)<br>3 / 6   |      |

| 0x70 | <b>BVS</b><br>(rel)<br>2 /<br>2** | <b>ADC</b><br>(indY)<br>2 / 5* |                              |      |                              | <b>ADC</b><br>(zpX)<br>2 / 4 | <b>ROR</b><br>(zpX)<br>2 / 6 |      | <b>SEI</b><br>(impl)<br>1 / 2 | <b>ADC</b><br>(absY)<br>3 / 4* |                               |      |                                | <b>ADC</b><br>(absX)<br>3 / 4* | <b>ROR</b><br>(absX)<br>3 / 7  |      |

| 0x80 |                                   | <b>STA</b><br>(indX)<br>2 / 6  |                              |      | <b>STY</b><br>(zp)<br>2 / 3  | <b>STA</b><br>(zp)<br>2 / 3  | <b>STX</b><br>(zp)<br>2 / 3  |      | <b>DEY</b><br>(impl)<br>1 / 2 |                                | <b>TXA</b><br>(impl)<br>1 / 2 |      | <b>STY</b><br>(abs)<br>3 / 4   | <b>STA</b><br>(abs)<br>3 / 4   | <b>STX</b><br>(abs)<br>3 / 4   |      |

| 0x90 | <b>BCC</b><br>(rel)<br>2 /<br>2** | <b>STA</b><br>(indY)<br>2 / 6  |                              |      | <b>STY</b><br>(zpX)<br>2 / 4 | <b>STA</b><br>(zpX)<br>2 / 4 | <b>STX</b><br>(zpY)<br>2 / 4 |      | <b>TYA</b><br>(impl)<br>1 / 2 | <b>STA</b><br>(absY)<br>3 / 5  | <b>TXS</b><br>(impl)<br>1 / 2 |      |                                | <b>STA</b><br>(absX)<br>3 / 5  |                                |      |

| 0xa0 | <b>LDY</b><br>(imm)<br>2 / 2      | <b>LDA</b><br>(indX)<br>2 / 6  | <b>LDX</b><br>(imm)<br>2 / 2 |      | <b>LDY</b><br>(zp)<br>2 / 3  | <b>LDA</b><br>(zp)<br>2 / 3  | <b>LDX</b><br>(zp)<br>2 / 3  |      | <b>TAY</b><br>(impl)<br>1 / 2 | <b>LDA</b><br>(imm)<br>2 / 2   | <b>TAX</b><br>(impl)<br>1 / 2 |      | <b>LDY</b><br>(abs)<br>3 / 4   | <b>LDA</b><br>(abs)<br>3 / 4   | <b>LDX</b><br>(abs)<br>3 / 4   |      |

| 0xb0 | <b>BCS</b><br>(rel)<br>2 /<br>2** | <b>LDA</b><br>(indY)<br>2 / 5* |                              |      | <b>LDY</b><br>(zpX)<br>2 / 4 | <b>LDA</b><br>(zpX)<br>2 / 4 | <b>LDX</b><br>(zpY)<br>2 / 4 |      | <b>CLV</b><br>(impl)<br>1 / 2 | <b>LDA</b><br>(absY)<br>3 / 4* | <b>TSX</b><br>(impl)<br>1 / 2 |      | <b>LDY</b><br>(absX)<br>3 / 4* | <b>LDA</b><br>(absX)<br>3 / 4* | <b>LDX</b><br>(absY)<br>3 / 4+ |      |

| 0xc0 | <b>CPY</b><br>(imm)<br>2 / 2      | <b>CMP</b><br>(indX)<br>2 / 6  |                              |      | <b>CPY</b><br>(zp)<br>2 / 3  | <b>CMP</b><br>(zp)<br>2 / 3  | <b>DEC</b><br>(zp)<br>2 / 5  |      | <b>INY</b><br>(impl)<br>1 / 2 | <b>CMP</b><br>(imm)<br>2 / 2   | <b>DEX</b><br>(impl)<br>1 / 2 |      | <b>CPY</b><br>(abs)<br>3 / 4   | <b>CMP</b><br>(abs)<br>3 / 4   | <b>DEC</b><br>(abs)<br>3 / 6   |      |

| 0xd0 | <b>BNE</b><br>(rel)<br>2 /<br>2** | <b>CMP</b><br>(indY)<br>2 / 5* |                              |      |                              | <b>CMP</b><br>(zpX)<br>2 / 4 | <b>DEC</b><br>(zpX)<br>2 / 6 |      | <b>CLD</b><br>(impl)<br>1 / 2 | <b>CMP</b><br>(absY)<br>3 / 4* |                               |      |                                | <b>CMP</b><br>(absX)<br>3 / 4* | <b>DEC</b><br>(absX)<br>3 / 7  |      |

| 0xe0 | <b>CPX</b><br>(imm)<br>2 / 2      | <b>SBC</b><br>(indX)<br>2 / 6  |                              |      | <b>CPX</b><br>(zp)<br>2 / 3  | <b>SBC</b><br>(zp)<br>2 / 3  | <b>INC</b><br>(zp)<br>2 / 5  |      | <b>INX</b><br>(impl)<br>1 / 2 | <b>SBC</b><br>(imm)<br>2 / 2   | <b>NOP</b><br>(impl)<br>1 / 2 |      | <b>CPX</b><br>(abs)<br>3 / 4   | <b>SBC</b><br>(abs)<br>3 / 4   | <b>INC</b><br>(abs)<br>3 / 6   |      |

| 0xf0 | <b>BEQ</b><br>(rel)<br>2 /<br>2** | <b>SBC</b><br>(indY)<br>2 / 5* |                              |      |                              | <b>SBC</b><br>(zpX)<br>2 / 4 | <b>INC</b><br>(zpX)<br>2 / 6 |      | <b>SED</b><br>(impl)<br>1 / 2 | <b>SBC</b><br>(absY)<br>3 / 4* |                               |      |                                | <b>SBC</b><br>(absX)<br>3 / 4* | <b>INC</b><br>(absX)<br>3 / 7  |      |

|      | 0x00                              | 0x01                           | 0x02                         | 0x03 | 0x04                         | 0x05                         | 0x06                         | 0x07 | 0x08                          | 0x09                           | 0x0a                          | 0x0b | 0x0c                           | 0x0d                           | 0x0e                           | 0x0f |

Table 3: outline of the complete instruction set of the MOS 6502 microprocessor.

The 6502 microprocessor has hardware and software interrupt features. If such an interrupt occurs the new program counter will be loaded from a "vector" address. Those are two memory locations forming a 16 bit memory value to address the complete 64K memory. It supports the following interrupts [15] [17]:

- **IRQ:** this maskable interrupt is hardware generated by a level change on the IRQ pin [18]. If the current instruction is executed, the processor will load the new program counter from the locations  $0 \times fffe$  and  $0 \times ffff$  and continue execution from there. If the "I" flag in the status register is set, the interrupt will be ignored. Also the two bytes of the program counter and the current processor status register are pushed onto the stack.

- **BRK:** is the same as an IRQ with the difference that it is triggered by software by the BRK instruction. In this case also the "B" flag in the status register will be set by this interrupt. This pushes also the two bytes of the program counter and the processor status register onto the stack. It is intended to use for debug purposes or as →system call feature.

- **NMI:** this is called the "non-maskable interrupt", because it cannot be masked out and occurs every time triggered. It is also triggered by the hardware NMI pin, when it changes from high to low [18]. Then the processor loads the new program counter from 0xfffa and 0xfffb. This pushes also the two bytes of the program counter and the processor status register onto the stack.

- **RESET:** also an hardware interrupt, triggered by the RESET pin. This interrupt resets the stack pointer to  $0 \times \text{fd}^3$  and loads the new program counter from  $0 \times \text{fffc}$  and  $0 \times \text{fffd}$ .

As the NMI interrupt cannot be turned of, it can interrupt a normal IRQ or BRK interrupt. This kind of interrupt was created for external devices that cannot even wait until the interrupt execution is finished, e.g. HSYNC or VSYNC of a  $\rightarrow$  CRT signal, which needs very proper timing.

The RESET interrupt is the strongest interrupt, causing the CPU to continue execution on the fetched address from the RESET vector. It resets the stack, so that one cannot return to the previous execution location by RTI.

#### Issues on the 6502 and further decisions

The fact that the MOS 6502 microprocessor is running until now in many devices properly does not imply that its free of mistakes or issues. There are many issues filed. Instead of listing all issues, only those which are important for this thesis are listed here:

• illegal opcodes: as mentioned before, the unused opcodes are not tied to something "neutral" in the original MOS 6502 microprocessor variant (later variants solved this issue). Because of the fact that most of them are undocumented and uncontrollable, the following decision is made: *only the by the*

<sup>3</sup> The SP gets reset to  $0 \times fd$ , because the 6502 injects a BRK instruction on RESET. While executing the BRK instruction it writes the two PC bytes and the processor status register onto the stack. In case of RESET the actual data is not needed so the control lines change to read while BRK tries to write onto the stack and no data is written onto the stack. Only the stack pointer decremented by three from  $0 \times ff$  [19] [20].

manual [17] and datasheet [15] specified and legal set of instructions is covered by this thesis (as seen in table 3).

"trouble" with JMP: the JMP instruction in indirect addressing mode has a bug. If the lower byte of the new program counter is on the last location of a page (e.g. 0x00ff), the next location is not the first location of the new page (e.g. 0x0100), the 6502 takes the first location of the current page (e.g. 0x0001) instead of the new page. This "mistake" will be considered in the emulator implementation.

# 2.1.2 Memory organisation

After explaining the key component – the 6502 microprocessor – one can move on with the Apple ][ system. Due to the fact that the processor can address 64K of memory, the Apple ][ could use up to 64K memory. The memory is further divided into two sections:

- the read and write section for user program space, from 0x0000 to 0xbfff. This are 48K of total memory available to the user (including the zero page and stack).

- a section for memory mapped I/O and expansion ROM from <code>0xc000</code> to <code>0xcfff</code>.

- the read only section stored in ROM modules from 0xd000 to 0xffff. These 12K bytes of memory are reserved for the monitor program and the Integer BASIC. The monitor program is a masterful program [21] (p. 40) that provides "system call" functions and controls the programs. The Integer BASIC is the "operating system" for the user providing a BASIC command line.

The following table 4 takes a detailed view on the memory showing a total overview in a graphical notation.

| Page(s)   | Size in<br>bytes | Intended function by the Apple ][                                                              |             |  |  |  |  |  |  |

|-----------|------------------|------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|--|

| 0x00      | 256              | Zero page for 6502 microprocessor (acceleration)                                               |             |  |  |  |  |  |  |

| 0x01      | 256              | 6502 microprocessor stack                                                                      |             |  |  |  |  |  |  |

| 0x02      | 256              | GETLN input buffer (Monitor program / BASIC)                                                   |             |  |  |  |  |  |  |

| 0x03      | 256              | Other monitor vector locations                                                                 |             |  |  |  |  |  |  |

| 0x04 0x07 | 1,024            | Primary "page" for text and low resolution (LoRes) graphics (see "LoRes graphics mode", p. 23) |             |  |  |  |  |  |  |

| 0x08 0x0b | 1,024            | Secondary page for text and LoRes graphics (double-buffer)                                     |             |  |  |  |  |  |  |

| 0x0c 0x1f | 5,120            |                                                                                                |             |  |  |  |  |  |  |

| 0x20 0x3f | 8,192            | Primary page for high resolution<br>(HiRes) graphics (see "HiRes graphics<br>mode", p. 23)     | Free to use |  |  |  |  |  |  |

| 0x40 0x5f | 8,192            | Secondary page for HiRes graphics<br>(double-buffer)                                           |             |  |  |  |  |  |  |

| 0x60 0xbf | 24,576           |                                                                                                |             |  |  |  |  |  |  |

| Page(s)     | Size in<br>bytes | Intended function by the Apple ][                                                                                                                                                                                                          |     |  |  |  |  |  |

|-------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

| 0xc0 … 0xcf | 4,096            | <ul> <li>Memory mapped I/O (no physical memory at all):</li> <li>important I/O locations at the beginning<br/>(e.g. graphics mode)</li> <li>peripheral card I/O space</li> <li>peripheral card ROM space</li> <li>expansion ROM</li> </ul> |     |  |  |  |  |  |

| 0xd0 0xf7   | 10,240           | BASIC language interpreter                                                                                                                                                                                                                 |     |  |  |  |  |  |

| 0xf8 … 0xff | 2,048            | Monitor program (inc. 6502 inter-<br>rupt vectors)                                                                                                                                                                                         | ROM |  |  |  |  |  |

|             | 65,536           | # of total memory locations                                                                                                                                                                                                                |     |  |  |  |  |  |

Table 4: Apple ][ memory map, all 256 pages and their function (if any) [21] (p. 69).

The pages  $0 \times c0$  to  $0 \times cf$  perform an important action: the memory mapped I/O. That means that this memory locations have no physical memory at all. Instead, the address on the address bus is used to trigger some kind of action. Mostly these locations are read and the result is an undefined value which is discarded, because referencing the specific memory location has performed the desired hardware action (e.g. beep with the speaker).

The memory mapped I/O section plays an important role. The following table outlines the general structure of this memory region:

|        | 0x0                                              | 0x1                                             | 0x2    | 0x3    | 0x4 | 0x5 | 0x6  | 0x7  | 0x8 | 0x9                      | 0xa | 0xb | 0xc | 0xd | 0xe | 0xf |

|--------|--------------------------------------------------|-------------------------------------------------|--------|--------|-----|-----|------|------|-----|--------------------------|-----|-----|-----|-----|-----|-----|

| 0xc000 | Keyb                                             | Keyboard data (see "2.1.4 The keyboard", p. 24) |        |        |     |     |      |      |     |                          |     |     |     |     |     |     |

| 0xc010 | Keyboard clear (see "2.1.4 The keyboard", p. 24) |                                                 |        |        |     |     |      |      |     |                          |     |     |     |     |     |     |

| 0xc020 | Cassette output toggle                           |                                                 |        |        |     |     |      |      |     |                          |     |     |     |     |     |     |

| 0xc030 | Spea                                             | ker to                                          | oggle  |        |     |     |      |      |     |                          |     |     |     |     |     |     |

| 0xc040 | Utilit                                           | y stro                                          | be     |        |     |     |      |      |     |                          |     |     |     |     |     |     |

| 0xc050 | gr                                               | tx                                              | no     | mix    | pri | sec | lore | hire | an0 |                          | an1 |     | an2 |     | an3 |     |

| 0xc060 | Game controller input, cassette input            |                                                 |        |        |     |     |      |      |     | 0xc060 – 0xc067 mirrored |     |     |     |     |     |     |

| 0xc070 | Gam                                              | e con                                           | trolle | r stro | be  |     |      |      |     |                          |     |     |     |     |     |     |

Table 5: important built-in I/O locations [21] (p. 79).

As one can see, these locations manage important I/O functions like the keyboard input or (sound) speaker output and other I/O related stuff. The 16 memory locations, beginning at  $0 \times c050$ , manage the graphic output of the entire Apple ][. The abbreviations have the following meanings:

- "gr" and "tx" stand for "graphics mode" and "text mode" and toggle between fullscreen graphics and fullscreen character display.

- "no" and "mix" decide whether the screen is "not mixed" or "mixed". In mixed mode together with graphics mode, the Apple ][ displays four lines of text mode on the lower section of the screen (e.g. to see graphics while entering BASIC commands).

- "pri" and "sec" decide which location for video data in memory is used the primary or the secondary. This can be used for frame double-buffering.

- "lore" and "hire" distinguish between the low resolution mode and high resolution mode.

- "an0" to "an3" are called "annunciator ports". These are simply digital output lines which can be turned off by referencing the lower address and on by referencing the higher address. This feature is useful to communicate to a serial device or something else.

Furthermore there is a difference between this memory locations. They are either a "toggle switch" or a "soft switch".

These toggle switches are internally flip-flops. Each time a read occurs the flip flop will change its state to the opposite (logical low or high). By reading this memory location the flip flow will be toggled. By writing to this location, the flip flop will be toggled twice and is finally in the same state as it was before. An example of a toggle switch is the speaker output. By reading the location it will "click". Performing this action faster and cyclic, a tone might be generated [21] (p. 20, p. 79).

Soft switches on the other hand are as simple as light switches with two states: every state has a memory location. If this location is invoked by a read or write<sup>4</sup>, the switch is thrown to this state [21] (p. 79). The video mode selection or annunciator ports are made out of soft switches: if a read occurs on  $0 \times c050$ , the Apple ][ output is forced to fullscreen graphics output. If  $0 \times c051$  is referenced, the Apple ][ is forced to fullscreen text output.

The Apple ][ had also eight extension card slots and the possibility to map their I/O registers and ROM code into the main memory (table 4). This enabled the first Apple ][ to use a disk drive although it was not yet invented when it was released. The disk drive came with an extension card, which was inserted in one of these slots. The driver firmware was mapped into the main memory place for peripheral cards ROM<sup>5</sup> and the user was able to work with the disk drive. As *important and interesting these features might be they are not covered deeper on this thesis, because they aren't implemented yet. An implementation would go beyond the scope of this thesis.*

As seen before, the user could work with their programs in a maximum of 48K bytes of memory. In those early days this "huge" amount of memory was very expensive. So the original Apple ][ was shipped containing 4K bytes of user memory [21] (p. 71). The motherboard contained 24 + 1 sockets for  $\rightarrow$ DIP RAM modules. The 24 sockets are split into tree "banks" or rows of eight sockets holding a static RAM  $\rightarrow$ IC and forming a byte, because a static RAM  $\rightarrow$ IC stored only bits, not bytes. The last socket was filled with jumpers to place the memory of the eight sockets inside the main memory at the right location. Every group of eight slots needs to contain the same memory modules, if used, to work properly [21] (p. 71).

With this flexible system and RAM modules available in 4 and 16 Kbit<sup>6</sup>, there are nine

<sup>4</sup> E.g. by using an assembler instruction onto this memory location, which will read it or write to it.

<sup>5</sup> From 0xc100 to 0xc7ff every peripheral card slot has 256 byte PROM (program ROM, e.g. the "driver") space and a card could request 2K expansion ROM from 0xc800 to 0xcfff [21].

<sup>6</sup> A module of 4 Kbit memory contains 4.096 distinct memory locations of one bit length (not one byte!). This is the reason, why they are grouped by eight: eight of these modules form a byte of data in the memory.

valid memory combinations: 4K, 8K, 12K, 16K, 20K, 24K, 32K, 36K and 48K [21] (p. 71). Inserting the RAM modules into the 24 sockets and setting the jumpers correctly enabled the user to extend the memory later on, since memory ICs were expensive in those days.

# 2.1.3 Video output

As described, the video RAM is mapped into the memory and it supports different types of video output:

- 1. **text mode –** the screen is filled with 960 characters.

- 2. **low resolution (LoRes) graphics mode –** the screen is filled with 1.920 colored blocks. Every block can have one of 16 colors of the Apple ][ color palette.

- 3. **high resolution (HiRes) graphics mode** the screen can display a 280 by 192 pixels wide image with 53.760 distinct dots. Every dot could possibly have one color out of six. But there are some special rules restricting this.

- 4. **mixed mode** in this mode one of the graphics modes is enabled and the lower four lines of the screen are set to text mode, e.g. showing the BASIC command line.

#### Text mode

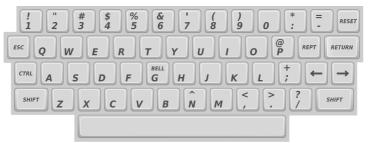

In the text mode the screen is filled with characters in 40 columns over 24 rows. Every character represents one memory value at the LoRes graphics memory page from  $0 \times 0400 - 0 \times 7 \text{fff}$  (or  $0 \times 800 - 0 \times 0 \text{bff}$  if secondary page selected).

A character consists of a 5 x 7 dot graphics with an one dot wide space on the left and the right and an one dot high line above every character to separate the lines. So every character is 7 x 8 dots in size. The character set consists of 64 characters:

|     | 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xa | 0xb | 0xc | 0xd | 0xe | 0xf |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0x0 | @   | А   | В   | С   | D   | Е   | F   | G   | Н   | I   | J   | К   | L   | М   | Ν   | 0   |

| 0x1 | Р   | Q   | R   | S   | Т   | U   | V   | W   | Х   | Y   | Z   | [   | ١   | ]   | ^   | _   |

| 0x2 |     | !   | "   | #   | \$  | %   | &   | ı   | (   | )   | *   | +   | ,   | -   |     | /   |

| 0x3 | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | :   | ;   | <   | =   | >   | ?   |

Table 6: the Apple ][ character set [22] (figure 8.4, chapter 8).

Each character has one byte of data and so it can represent 256 distinct symbols. The character set with its 64 characters is repeated four times inside this 256 distinct symbols. This enables different kinds of displays for every character set block:

- 0x00 0x3f (0b00\*\*\*\*\*): the characters are displayed inverse (black characters on white background)

- 0x40 0x7f (0b01\*\*\*\*\*): the characters are flashing. They are changing fast from inverse to normal display.

- 0x80 0xbf (0b10\*\*\*\*\*): normal character display (white on black).

- 0xc0 0xff (0b11\*\*\*\*\*): repetition of the previous block.

The memory layout on the display page is quite complex and fragmented – the character rows have free memory locations as spacers. *In order to stay in the scope of this document, this is not covered detailed. More information can be found at* [21] (p. 18, fig. 2).

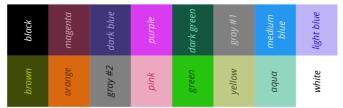

#### LoRes graphics mode

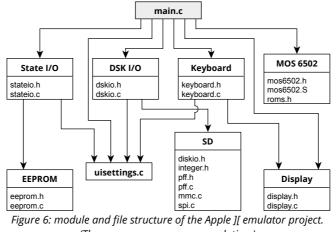

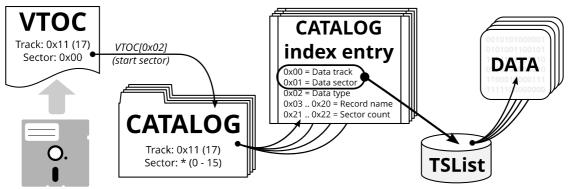

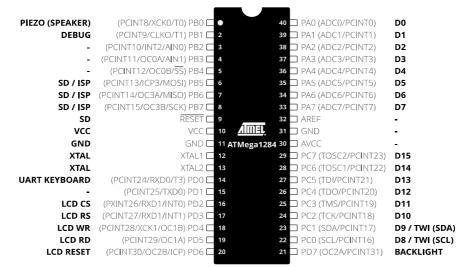

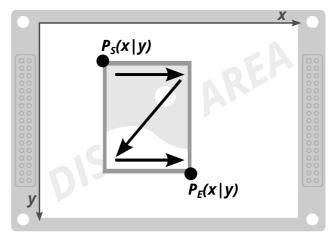

In the low resolution mode the screen is filled with 1,920 colored blocks, each is  $7 \times 4$  pixels in size. This leads to a resolution of 40 x 48 blocks. Every block can have one of 16 colors.